International Advanced Research Journal in Science, Engineering and Technology ISO 3297:2007 Certified

IARJSET

Vol. 3, Issue 12, December 2016

# A Novel Logic Style used for Leakage Power Reduction in MOS Integrated Circuit

## Abhijeet Washishtha<sup>1</sup>, Tina Raikwar<sup>2</sup>

M. Tech Scholar, Department of Electronics and Communication Engineering, NIIST Bhopal, India<sup>1</sup>

Assistant Professor, Department of Electronics and Communication Engineering, NIIST Bhopal, India<sup>2</sup>

Abstract: Full adders are necessary parts in applications corresponding to digital signal processors (DSP) architectures and microprocessors. Additionally to its main task, that is adding 2 numbers, it participates in several different helpful operations appreciate subtraction, multiplication, division, address calculation, etc. In most of those systems the adder lies in the critical path that determines the general speed of the system. Therefore enhancing the performance of the 1-bit full adder cell (the building block of the adder) could be a significant goal. Demands for the low power VLSI approaching the expansion of insistent design process to control use severely. To accomplish the rising demand, we advise a new low power adder by give up the MOS transistor calculate that reduce the grave threshold defeat so anew enhanced 14T CMOS 1-bit full adder cell is specified in this paper. Results show five hundredth improvement in threshold loss drawback, 45% improvement in speed and considerable power consumption over the given adder and other different types of adders with comparable presentation.

Keywords: Arithmetic circuit, full adder, multiplier, low power, very Large-scale integration (VLSI).

#### I. INTRODUCTION

In practically all digital Integrated Circuit designs today, the addition procedure is one of the mainly necessary and frequent procedures. Instruction set for DSP's and allpurpose reason processors consist of at least one category of addition. Other commands like subtraction and multiplication make use of addition in their procedure and their underlying hardware is alike if not equal to addition hardware. Often, an Adder or multiple adders will be in the critical path of the preparation, hence the management of a recommend Will be often be limited by the performance of its adders.

When the designers look at further element of a chip, such as region or control, will find that the Hardware for addition will be a large contributor to these areas. It is then of assistance to choose the correct adder to implement in a design for the reason that the many feature it aspects in the overall chip. In this section we have reviewed several types of adders and studied their operation and performance. The various types of adders are

- Basic Adder Units

- Half adder

- Full adder

- Parallel Adders

- Ripple carry adder

- Carry look ahead adder.

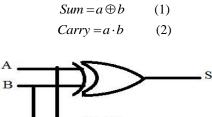

A combinational circuit that adds two bits is known as a half adder. The half adder adds two single A and B Binary digits has two outputs, sum (S) and carry (C). With the combinational of an OR gate to join their carry outputs, two half adders be able to combined to create a full adder. Equations are the Boolean equations for sum and carryout.

Fig. 1. Gate Schematic for Half Adder

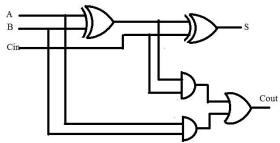

C

A full adder joins three bits, the third bit produced from a preceding addition operation. A full adder combines binary figures and accounts for values carried in as well as out. A one-bit full adder join three one-bit numbers, frequently written as A, B, and Cin; operands are A and B, and Cin is a bit carried in from the next less considerable step.

$$\begin{split} \mathbf{S} &= \mathbf{A} \oplus \mathbf{B} \oplus \mathbf{C}_{\text{in}} \quad (3) \\ \mathbf{C}_{\text{out}} &= (\mathbf{A}, \, \mathbf{B}) + (\mathbf{C}_{\text{in}} \boldsymbol{.} \, (\mathbf{A} \oplus \mathbf{B})) \quad (4) \end{split}$$

Fig. 2 Schematic symbol for a 1 bit FA

## IARJSET

International Advanced Research Journal in Science, Engineering and Technology ISO 3297:2007 Certified

Vol. 3, Issue 12, December 2016

### II. METHOD

The Significant effort has been dedicated to explore new logic designs that transcend dynamic domino logic and CDL. Above all, source-coupled logic (SCL) has shown superior performance that's troublesome to realize exploitation the other logic vogue. However, it suffers from high power dissipation because of constant current draw and its differential nature needs complementary signals. Pseudo-nMOS logic, that uses one pMOS junction transistor as a pull-up device, provides high speed and low junction transistor count at the expense of high static power consumption moreover as reduced output voltage swing. Output prediction logic (OPL) has additionally shown superior performance in high speed adders. However, OPL needs the generation and distribution of multi-phase clock signals with little temporal arrangement separations and low skews that is troublesome to realize. whereas varied high speed logic designs are planned, dynamic and CDL still stay the foremost engaging selections once performance is that the primary concern. Designers of digital circuits usually need quickest

performance. This implies that the circuit desires high clock frequency. Because of the continual demand of increase operative frequency, energy economical logic vogue is usually vital in VLSI. Dynamic logic circuits are necessary because it provides higher speed and has lesser junction transistor demand in comparison to static CMOS logic circuits. CD logic provides an area window technique and a self-reset circuit that permits strong logical operation with decreased power consumption. The foremost distinct characteristic of CD logic from previously planned logic designs are that the delay. Unlike SCL, CD logic doesn't need complementary signals and might be simply integrated with static and dynamic domino logics. Also, CD logic doesn't have the matter of constant static power dissipation almost like pseudonMOS. Moreover, the clock temporal arrangement demand of CD logic isn't as demanding as OPL. CD logic can do strong operation with best performance as long as CLK signal arrives before the input signals. Constant delay (CD) logic vogue has been designed to mitigate the matter of high speed and noise margined.

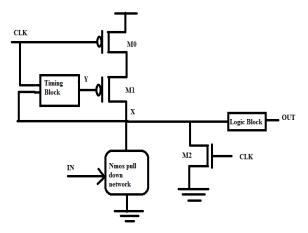

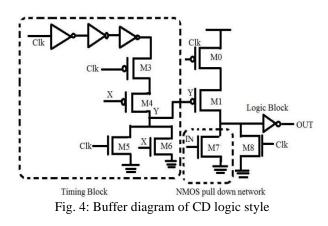

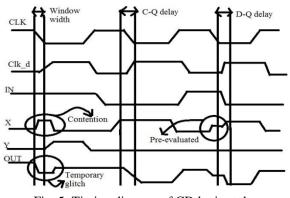

Fig. 3: Constant delay logic style

It outperforms different logic designs with higher energy potency. This high performance energy economical logic vogue has been wont to implement sophisticated logic expressions. It exhibits a novel characteristic wherever the output is pre-evaluated before the input from the preceding stage is prepared. Constant delay logic vogue that is employed for top speed applications is shown in Fig.3.

CD logic consists of 2 additional blocks. They're the timing block (TB) also because the logic blocks (LB). Temporal arrangement block consists of self reset technique and window adjustment technique. This allows strong logical operation with lower power consumption and better speed. Logic block reduces the unwanted defect and additionally makes cascading CD logic possible. The distinctive characteristic of this logic is that the output is pre- evaluated before the inputs from the preceding stage got prepared [3].

The temporal order diagram for constant delay logic is shown in Fig. 5. CD logic works below 2 modes of operation.

i. Pre-discharge mode (CLK=1) ii. Analysis mode (CLK=0)

Fig. 5: Timing diagram of CD logic style

Pre-discharge mode happens once CLK is high and analysis mode happens once CLK is low. Throughout predischarge mode X and OUT are pre-discharged and precharged to GND and VDD severally. Throughout analysis mode 3 totally different conditions particularly contention, C-Q delay and D-Q delay takes place within the CD logic.

## ISSN (Online) 2393-8021 ISSN (Print) 2394-1588 IARJSET International Advanced Research Journal in Science, Engineering and Technology ISO 3297:2007 Certified

Vol. 3, Issue 12, December 2016

delay (clock-out) happens once IN goes to zero before also the delay is measured from IN to Out. CLK transits to low. At now X rises to logic one and OUT

Contention mode happens once IN=1 for the complete is discharged to VDD and also the delay is measured from analysis amount. Throughout now a right away path CLK to Out. D-Q delay happens once IN goes to zero current flows from pMOS to PDN. X raises to nonzero when CLK transits to low. Throughout now X initially voltage level and OUT experiences a short lived bug. C-Q enters contention mode and later rises to logic one and

## **III.RESULT**

The maximum voltage is applying 5V to each circuit. The clock pulse is having the maximum amplitude of +5V to -5V.

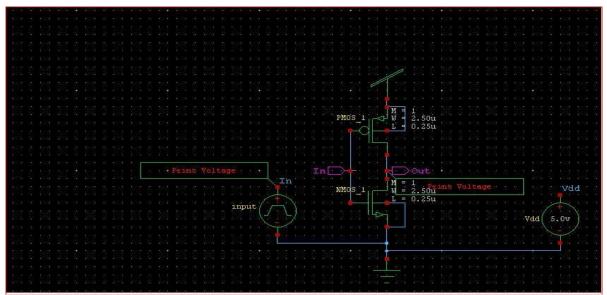

Fig. 6:- Schematic of Inverter

Fig. 7:- Output waveform of an inverter

## International Advanced Research Journal in Science, Engineering and Technology

**IARJSET**

ISO 3297:2007 Certified

Vol. 3, Issue 12, December 2016

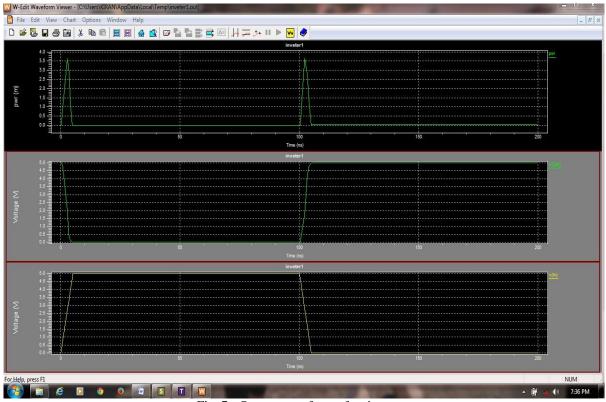

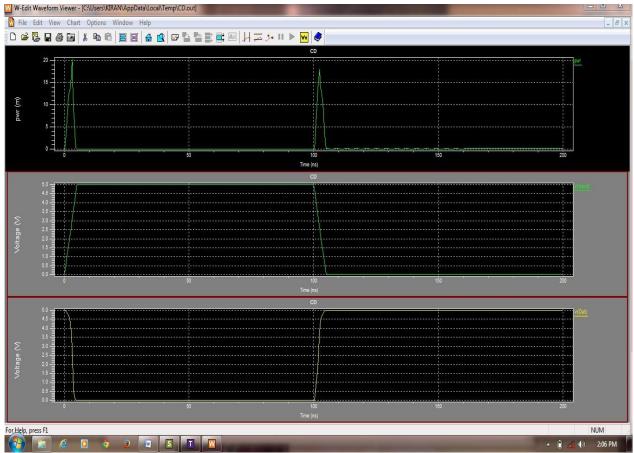

Fig. 8:- CD Inverter schematic

Fig. 9:- Output waveform of CD Inverter

# **IARJSET** International Advanced Research Journal in Science, Engineering and Technology

ISO 3297:2007 Certified

Vol. 3, Issue 12, December 2016

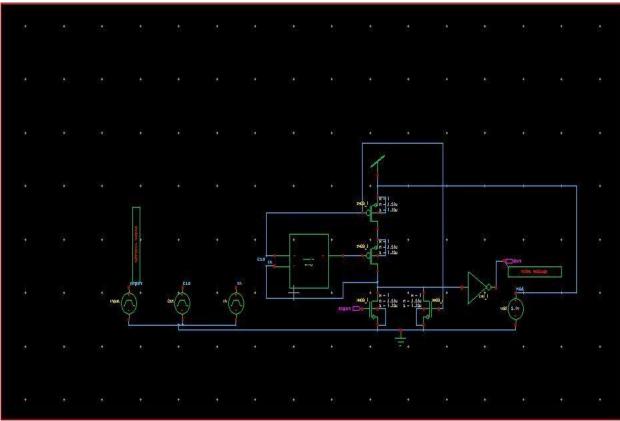

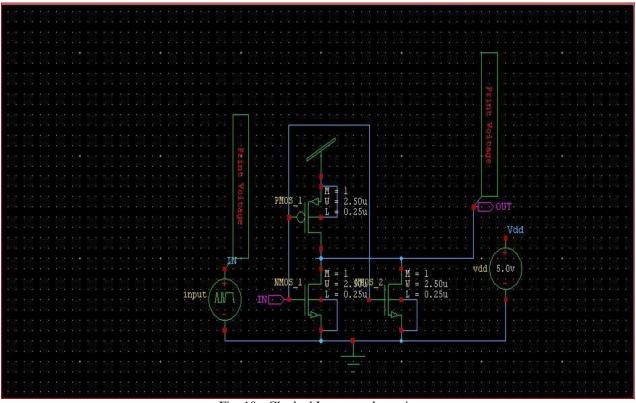

Fig. 10:- Clocked Inverter schematic

Fig. 11:- Output waveform of a Clocked Inverter

# **IARJSET**

International Advanced Research Journal in Science, Engineering and Technology ISO 3297:2007 Certified

Vol. 3, Issue 12, December 2016

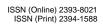

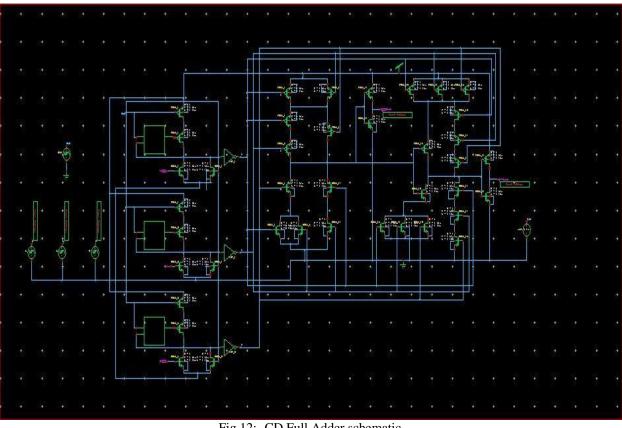

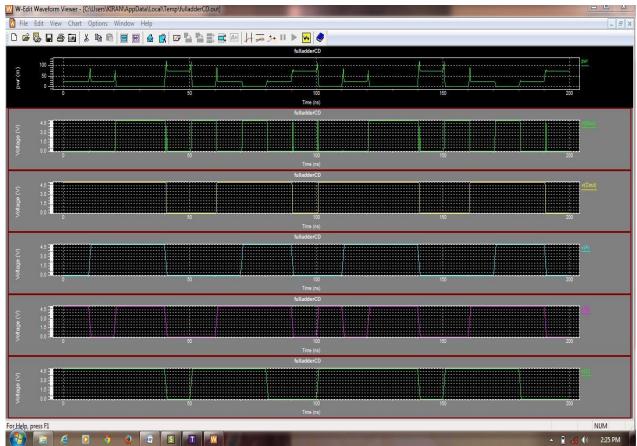

Fig.12:- CD Full Adder schematic

Fig. 13:- Output of a CD Full Adder

## International Advanced Research Journal in Science, Engineering and Technology ISO 3297:2007 Certified

IARJSET

Vol. 3, Issue 12, December 2016

International Advanced Research Journal in Science, Engineering and Technology ISO 3297:2007 Certified

IARJSET

Vol. 3, Issue 12, December 2016

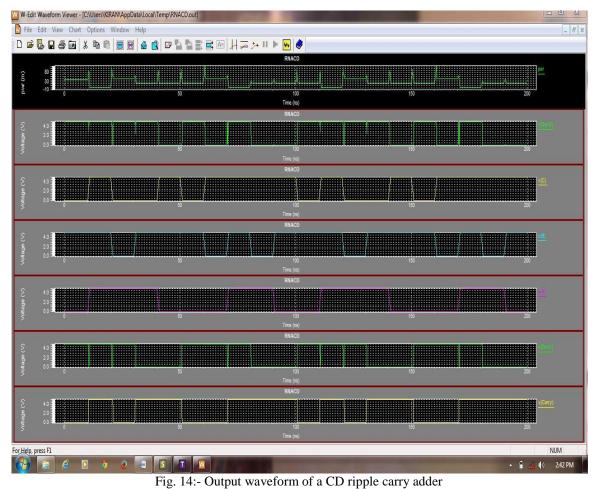

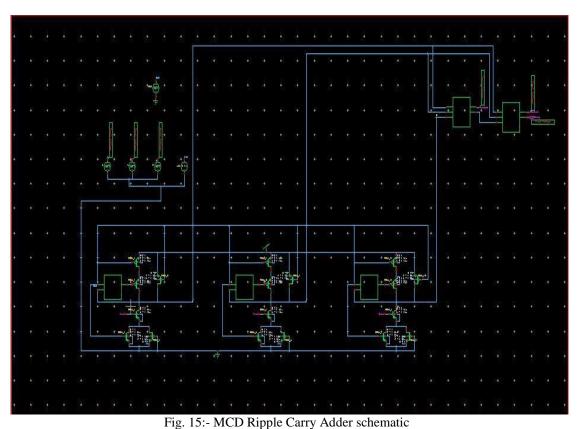

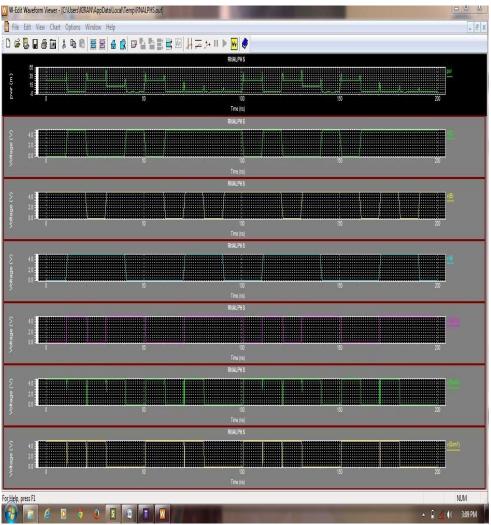

Fig. 16:- Output waveform of a MCD Ripple Carry Adder

#### **IV.CONCLUSION**

To overcome from the whole problem, changed constant delay logic vogue is planned. It will increase higher energy potency, performance and reduces the delay by exploitation the Tanner EDA software system. A brand new high performance changed constant delay logic vogue [4] and Clocked logic vogue was planned. It will increase performance and reduces the facility as compared to the Constant delay logic vogue. Adders are designed exploitation each existing as well as planned logic. It is simulated in CMOS technologies for examination <sup>[6]</sup> performance parameter power, rise-time and fall-time. From the result it's found that MCD and Clocked logic vogue has higher power than the present logic vogue.

#### REFERENCES

- [1] Jatin N. Mistry, James Myers, Bashir M. Al-Hashimi, David Flynn, John Biggs and Geoff V. Merrett, "Active Mode Sub clock Power Gating", IEEE transaction on VLSI system, Vol. 22, no. 9, Sep. 2014.

- Shruti Mehrotra, Satwik Patnaik & Manisha Pattanaik, "Design [2] Technique for Simultaneous Reduction of Leakage Power and [10] Contention Current for Wide fan-in Domino Logic Based 32:1

Multiplexer Circuit", Proceedings of 2013 IEEE Conference on Information and Communication Technologies (ICT 2013).

- [3] P. Chuang, David Li and Manoj Sachdev., "Constant Delay Logic Style," IEEE Transactions on Very Large Scale Integration Systems. Vol.21, No.3, pp. 554-565, March 2013.

- Pierce-Jen Chuang, David Li, Manoj Sachdev, and Vincent Gaudet, "A 148ps 135mW 64-bit Adder with Constant-Delay Logic in 65nm CMOS", IEEE trans. 2012.

- [5] J. Seomun, I. Shin, and Y. Shin, "Synthesis of active-mode power gating circuits," IEEE Trans. Comput.- Aided Design Integr. Circuits Syst., vol. 31, no. 3, pp. 391–403, Mar. 2012. N. Mehta and B. Amrutur, "Dynamic supply and threshold voltage

- scaling for CMOS digital circuits using insitu power monitor,' IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 20, no. 5, pp. 892-901, May 2012.

- [7] Y. Wang, S. Roy, and N. Ranganathan, "Run-time power-gating in caches of GPUs for leakage energy savings," in Proc. DATE Conf., Mar. 2012, pp. 300-303.

- [8] A. Weddell, D. Zhu, G. V. Merrett, S. P. Beeby, and B. M. Al-Hashimi, "A practical self-powered sensor system with a tunable vibration energy harvester," in Proc. Int. Workshop Micro Nano-Technol. Power Generation Energy Convers. Appl., Dec.2012, pp. 14.

- [9] K. Yelamarthi and C.I.H.Chen, "Delay Optimization Considering Power Saving in Dynamic CMOS Circuits", IEEE Int. Symp. Quality Electronic Des. (ISQED), pp. 1-6, Mar 2011. Hao Xu, Ranga Vemuri, and Wen-Ben Jone,

- "Dynamic Characteristics of Power Gating During Mode Transition", IEEE

## IARJSET

International Advanced Research Journal in Science, Engineering and Technology ISO 3297:2007 Certified

Vol. 3, Issue 12, December 2016

transactions on very large scale integration (VLSI) system, vol. 19, no . 2, Feb. 2011.

- [11] Ashoka Sathanur, Luca Benini, Alberto Macii, Enrico Macii, and Massimo Poncino, "Row-Based Power-Gating: A Novel Sleep Transistor Insertion Methodology for Leakage Power Optimization in Nanometer CMOS Circuit", IEEE transactions on very large scale integration (VLSI) system, vol. 19, no. 3, March 2011.

- [12] Houman Homayoun, Avesta Sasan, Alexander V. Veidenbaum, Hsin-Cheng Yao, Shahin Golshan, and Payam Heydari, "MZZ-HVS: Multiple Sleep Modes Zigzag Horizontal and Vertical Sleep Transistor Sharing to Reduce Leakage Power in On-Chip SRAM Peripheral Circuits", IEEE transactions on very large scale integration (VLSI) system, Vol. 19, no. 12, Dec. 2011.

- [13] M. Aguirre-Hernandez and M. Linares-Aranda, "CMOS fulladders for energy-efficient arithmetic applications," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 19, no. 99, pp. 1–5, Apr. 2010.

- [14] B. Zeydel et al., "Energy-Efficient Design Methodologies: High-Performance VLSI Adders," IEEE Journal of Solid-State Circuits, vol. 45, no. 6, pp. 1220–1233, June 2010.

- [15] H.F.Dadgour, K.Banerjee, "A Novel Variation-Tolerant Keeper Architecture for High-Performance Low- Power Wide Fan-In Dynamic OR Gates", IEEE Trans. Very Large Scale Integr.(VLSI) Syst. vol. 18, no. 11, pp. 1567-1577, Nov. 2010.

- [16] D. Juan and Y. Chen and M. Lee, and S. Chang, "An efficient wakeup strategy considering spurious glitches phenomenon for power gating designs," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 18, no. 2, pp. 246–255, Feb. 2010.

- [17] R. Zlatanovici et al., "Energy–Delay Optimization of 64-Bit Carry-Look ahead Adders With a 240ps 90 nm CMOS Design Example," IEEE Journal of Solid-State Circuits, vol. 44, no. 2, pp. 569–583, Feb. 2009.

- [18] H. Xu, W.-B. Jone, and R. Vemuri, "Dynamic virutal ground voltage estimation for power gating," in Proc. ISLPED, Aug. 2008, pp. 27–32.

[19] H. Xu, R. Vemuri, and W. Jone, "Accurate energy breakeven time

- [19] H. Xu, R. Vemuri, and W. Jone, "Accurate energy breakeven time estimation for run-time power gating," in Proc. ICCAD, Jul. 2008, pp. 161–168.

- [20] A. Calimera et al., "Optimal MTCMOS reactivation under power supply noise and performance constraints," Proc. DATE-08: Design Automation and Test in Europe, pp. 973–978, Mar. 2008.